【導讀】隨著集成電路設計邁入超大規模時代,芯片規模已從早期小規模集成電路的數千門級,躍升至當前先進制程下的數十億門級。這一指數級增長不僅帶來了功能復雜度的爆發式提升,更使芯片驗證環節面臨“驗證鴻溝”——傳統基于仿真的驗證手段,因算力消耗大、迭代周期長,難以覆蓋超大規模設計的全功能場景,無法滿足產品快速上市對高效、精準驗證的需求。

隨著集成電路設計邁入超大規模時代,芯片規模已從早期小規模集成電路的數千門級,躍升至當前先進制程下的數十億門級。這一指數級增長不僅帶來了功能復雜度的爆發式提升,更使芯片驗證環節面臨“驗證鴻溝”——傳統基于仿真的驗證手段,因算力消耗大、迭代周期長,難以覆蓋超大規模設計的全功能場景,無法滿足產品快速上市對高效、精準驗證的需求。

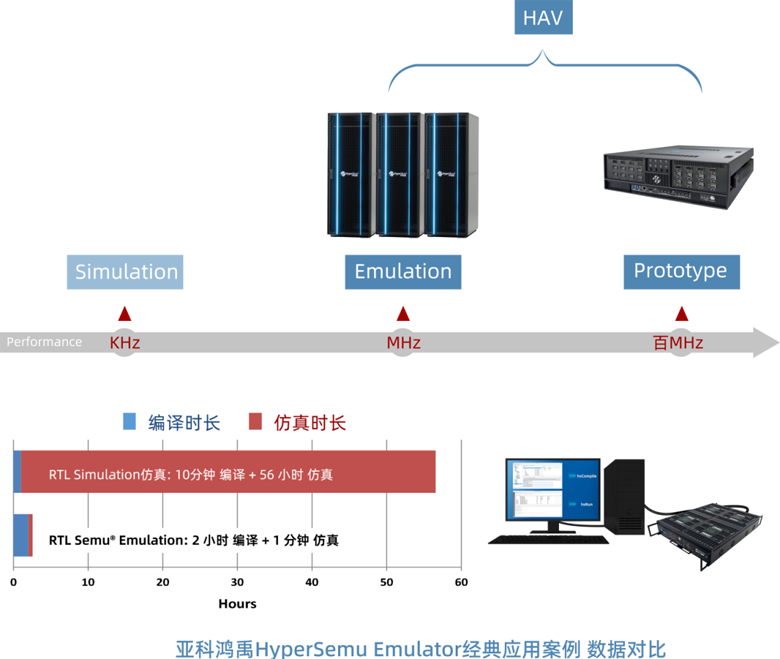

在此背景下,硬件輔助驗證(HAV: Hardware-Assisted Verification)憑借其接近真實芯片的運行速度和全功能映射能力,成為彌合這一鴻溝的核心技術,而將芯片設計高效映射到驗證芯片陣列的“分割技術”,則是決定硬件輔助驗證性能的關鍵。

硬件輔助驗證分割:從需求到核心價值

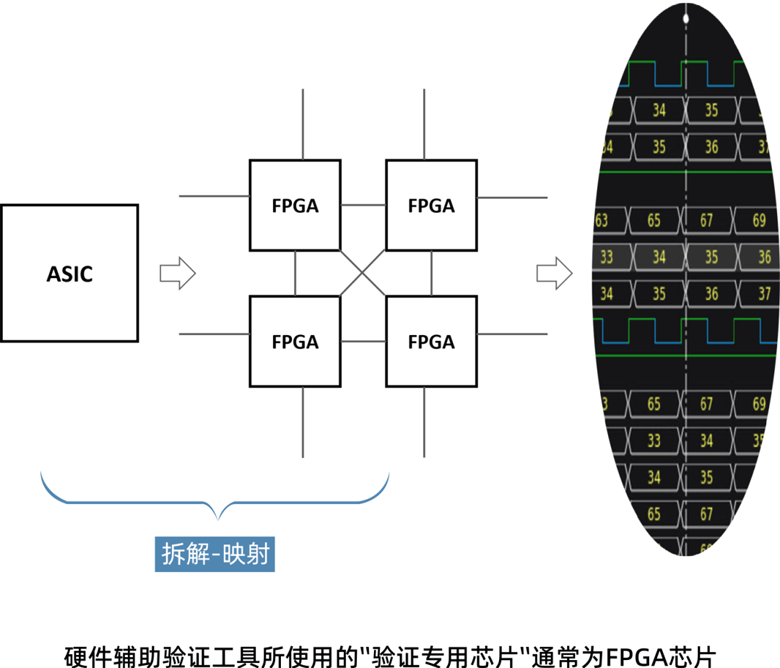

硬件輔助驗證的核心邏輯,是將超大規模芯片的RTL(寄存器傳輸級)設計,拆解為多個可適配單顆驗證專用芯片(通常為FPGA芯片)資源的子模塊,再通過驗證芯片陣列的協同工作,模擬真實芯片的功能與應用環境。這一“拆解-映射”過程即為分割,其本質是解決“超大規模設計”與“單顆驗證芯片有限資源”之間的矛盾。

分割的質量直接決定硬件輔助驗證的最終效果:

優質分割:可實現驗證芯片資源(邏輯單元、存儲單元、I/O引腳)的均衡利用,最大限度減少跨驗證芯片的信號交互(即“割邊”),降低關鍵路徑延時,保障硬件輔助驗證的高工作頻率,同時減少人工調整成本。

劣質分割:會導致部分驗證芯片資源過載(需手動刪減功能)、部分資源閑置,或跨驗證芯片割邊過多。前者可能引入功能性錯誤,后者會因外部連線延時增加,大幅拉低驗證頻率,甚至無法滿足軟件調試對實時性的需求。

經典圖分割算法:大規模設計分割的基礎框架

芯片設計的分割問題,在數學模型上可轉化為“圖分割”——將芯片的模塊(節點)與模塊間的信號連接(邊,含權重)構成的圖,拆分為多個子圖,且需滿足“分區資源平衡”(各子圖適配單顆驗證芯片資源)與“割邊最小”(減少跨驗證芯片信號交互)兩大目標。

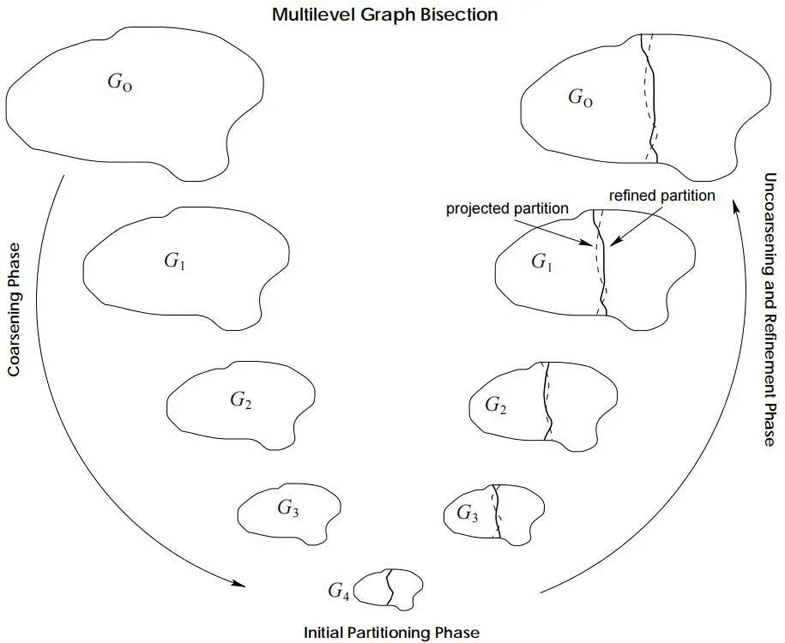

主流的“多層次圖劃分”框架,通過“粗化-初始劃分-細化”三步流程,高效解決大規模圖分割問題,其核心邏輯如下:

粗化(Coarsening):簡化規模,保留核心結構

核心目標:將百萬級節點的原始設計圖,通過迭代合并,逐步壓縮為數千級節點的“粗化圖”,在降低后續計算復雜度的同時,完整保留原圖中“高權重邊”(如關鍵信號連接)和”緊密關聯節點”(如同一功能模塊的子模塊)的結構特征。

實現邏輯:采用“節點匹配”策略,優先合并滿足以下條件的節點:

?節點間邊的權重高(信號交互頻繁)

?節點的資源屬性相似(如均為邏輯運算模塊,或均為存儲模塊)

?合并后不破壞局部功能完整性(如不拆分一個完整的運算單元)

每輪合并后生成“超節點”(由多個原始節點構成)和“超邊”(由超節點間的原始邊合并而成),最終形成一系列規模遞減的粗化圖。

初始劃分(Initial Partitioning):為粗圖制定基礎方案

核心目標:在規模最小的粗化圖上生成首個滿足“資源平衡”與“割邊最小”的分區方案,為后續細化提供起點。

常見算法:

?隨機劃分:將粗化圖的超節點隨機分配到目標分區(分區數量=驗證芯片數量),優點是計算速度快,可作為基礎方案;缺點是割邊較多,需后續優化

?貪心劃分:基于“局部最優”原則,優先將連接緊密(超邊權重高)的超節點分配到同一分區,逐步減少跨區超邊數量。例如,先將權重最高的超邊連接的兩個超節點劃入同一分區,再以該分區為核心,逐步吸納相鄰的高權重超節點,最終實現初步的平衡劃分

細化(Uncoarsening/Refinement):反向映射,優化分區質量

核心目標:將初始劃分方案從最小粗化圖,逐步“反向映射”回原始圖(即從超節點拆解為原始節點),并在每一步映射中優化分區,最終提升原始設計圖的分割精度——進一步減少割邊數量,同時確保各分區的資源完全平衡。

核心算法:FM算法(Fiduccia-Mattheyses):

?計算“增益”:對每個待移動的節點,計算其從當前分區移動到目標分區后,“割邊權重減少量”(正增益)與“資源平衡破壞度”(負增益)的差值,即“凈增益”

?選擇最優移動:優先移動凈增益最大的節點,直到無法通過移動節點提升分區質量(如所有節點移動的凈增益均為負)

?迭代優化:每完成一輪粗化圖到更細一級圖的映射,就執行一次FM算法優化,確保分區質量隨圖規模的擴大而持續提升

“多層次圖劃分”框架三步流程示意圖

時序驅動分割:突破頻率瓶頸的關鍵優化

經典圖分割算法以“割邊最少”為核心目標,但在硬件輔助驗證中,驗證工作頻率才是最終衡量標準——頻率過低會導致軟件調試周期延長,甚至無法模擬芯片的真實運行場景。而頻率的核心制約因素是“關鍵路徑延時”,因此需要在傳統圖分割框架中引入“時序”維度,形成“時序驅動分割算法”。

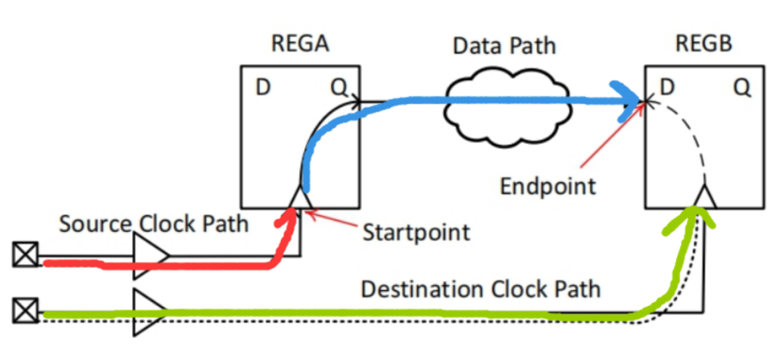

時序路徑與關鍵路徑

時序路徑:芯片中信號從起點(如輸入端口、寄存器時鐘端)到終點(如輸出端口、寄存器數據端)的傳播路徑,其延時由路徑上所有邏輯單元(如與門、觸發器)的延時之和決定。

時序路徑示意圖

關鍵路徑(Critical Path):所有時序路徑中,延時最長的路徑。它直接決定芯片的最高工作頻率——時鐘周期必須大于等于關鍵路徑的延時,否則信號無法在規定時間內到達終點,會違反寄存器的“建立時間”要求,導致電路功能錯誤。

時序驅動分割的核心策略

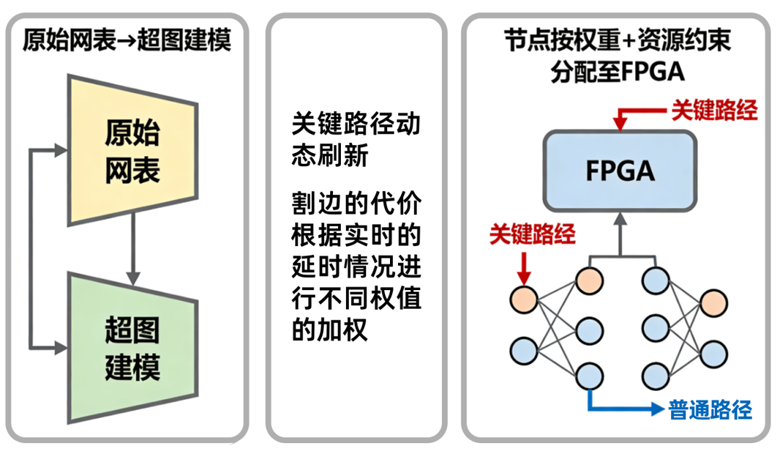

時序驅動分割的本質,是在“資源平衡”、“割邊最少”的基礎上,增加“關鍵路徑延時最小”的目標,通過以下優化貫穿分割全流程:

粗化階段:強化關鍵路徑的節點關聯

對關鍵路徑上的節點,提升其“合并優先級”——即使這些節點的邊權重并非最高,也優先將其合并為同一超節點,避免后續劃分時被拆分到不同驗證芯片,從而減少關鍵路徑上的跨驗證芯片割邊(跨驗證芯片連線的延時遠大于驗證芯片內部連線)

細化階段:優先優化關鍵路徑的割邊

調整FM算法的“增益計算邏輯”:對關鍵路徑上的割邊,賦予更高的權重——移動關鍵路徑相關節點時,若能減少關鍵路徑上的割邊,其“凈增益”會被額外提升,從而優先被選擇移動,最大限度減少關鍵路徑上的跨驗證芯片信號交互

結合時分復用(TDM)的特殊優化

TDM技術的作用與矛盾:當跨驗證芯片割邊數量超過驗證芯片的I/O引腳數量時,需通過時分復用(Time Division Multiplexing) 技術,讓多個割邊信號“輪流使用”同一組I/O引腳(即劃分不同時間時隙傳輸),從而解決物理連線不足的問題。但TDM會增加信號延時(每個信號需等待其專屬時隙),且TDM比率越高(共享同一引腳的信號越多),延時越大

時序驅動的TDM優化策略:

?對關鍵路徑上的割邊信號,禁用TDM或采用最低TDM比率(如1:1,即無復用),避免額外延時疊加

?對非關鍵路徑上的割邊信號,可適當提高TDM比率,節省I/O引腳資源,在不影響整體頻率的前提下滿足連線需求

亞科鴻禹的時序驅動分割方案:技術特色與實踐價值

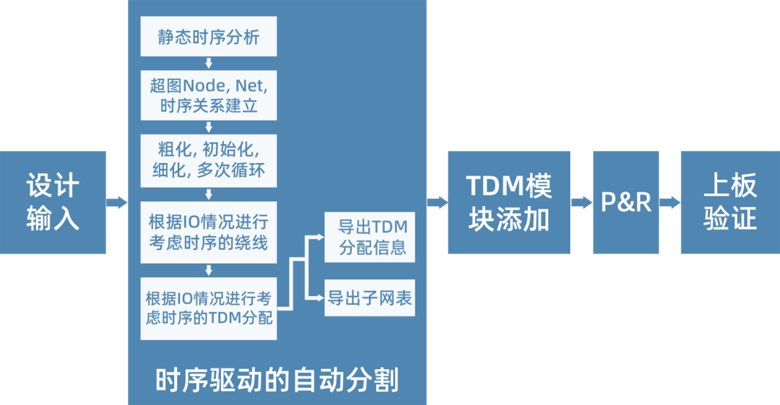

針對超大規模芯片的硬件輔助驗證需求,亞科鴻禹基于上述技術原理,開發了定制化的時序驅動分割流程,核心特色如下,可有效提升分割效率與硬件輔助驗證頻率:

定制化分割引擎:內存高效,支撐更優算法

分割引擎基于時序網表的結構特點,采用定制化的數據存儲架構,這使得引擎能在有限硬件資源下,加載更大規模的設計圖(如輕松加載十億門級),同時有更多內存余量嘗試更復雜的優化算法(如多輪迭代的FM算法),為尋找最優分割結果奠定基礎

全時序路徑動態刷新:實時適配時序需求

分割過程中,實時動態刷新所有時序路徑的延時數據(而非僅依賴初始時序分析結果),可精準捕捉分割調整對時序的影響——例如,某一節點移動后,不僅更新其所在路徑的延時,還會聯動更新關聯路徑的時序狀態,確保分割策略始終貼合最新的時序需求,避免因時序信息滯后導致的優化偏差

自動優化跳數與TDM比率:平衡資源與時序

?自動分析分割后的“信號跳數”(信號從源節點到目標節點經過的驗證芯片數量),優先減少關鍵路徑的跳數(跳數越多,跨驗證芯片延時越大)

?結合時序要求,智能分配TDM比率:對關鍵路徑信號默認禁用TDM,對非關鍵路徑信號根據I/O資源情況自動計算最優TDM比率(如2:1或8:1),在滿足連線需求的同時,最大限度降低時序損耗

用戶干涉的自動分割模式:兼顧自動化與靈活性

支持“自動分割為主、用戶干預為輔”的模式:用戶可根據實際需求(如某一模塊需固定在特定驗證芯片上、某一信號需優先保障時序),預先設置約束條件(如節點分區鎖定、信號TDM比率限制),分割引擎會在約束范圍內自動優化,既減少人工調整成本,又能滿足定制化驗證需求

超大規模設計支持:應對多FPGA陣列場景

可支持數十億門級設計的分割任務,最多適配數百片驗證芯片構成的陣列,且能通過“分層分割”策略(先將整體設計拆分為多組子系統,再對每組子系統進行FPGA級分割),確保大規模陣列的協同工作效率,滿足先進制程SoC(系統級芯片)的硬件輔助驗證需求

亞科鴻禹HAV平臺時序驅動分割方案框圖

總結

在超大規模芯片設計的征程中,硬件輔助驗證的分割技術已然完成了從簡單資源分配到復雜系統工程的華麗轉身。經典多層次圖分割框架搭建起了分割的基礎邏輯架構,時序驅動的優化策略如關鍵路徑優先、TDM智能適配等成功突破頻率限制。亞科鴻禹推出的定制化分割方案,憑借內存高效利用、時序動態更新以及用戶靈活操作等獨特優勢,進一步提升了分割的效率與適配程度,為超大規模芯片的快速驗證筑牢了堅實根基,助力芯片產業在超大規模時代穩健前行。

推薦閱讀: